**Discontinued Product**

**OKI** Semiconductor

This version: Nov. 1998

# ML60851A

# USB Device Controller

# **GENERAL DESCRIPTION**

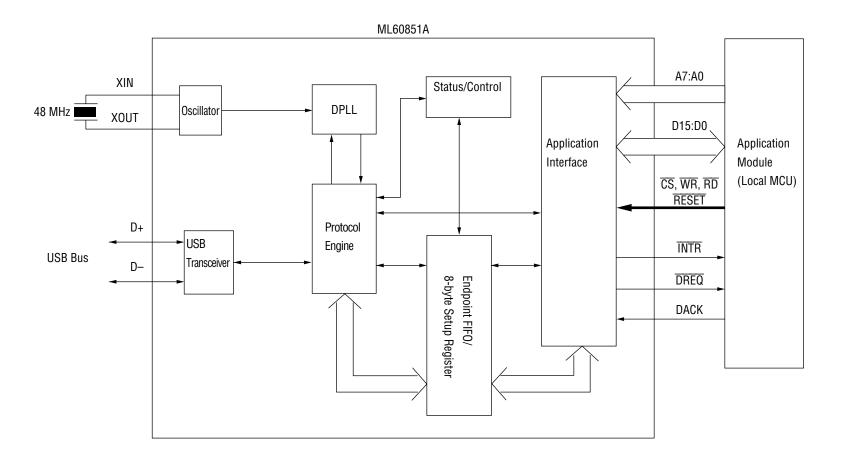

The ML60851A is a general purpose Universal Serial Bus (USB) device controller. The ML60851A provides a USB interface, control/status block, application interface, and FIFOs. The FIFO interface and two types of transfer have been optimized for BulkOut devices such as printers and BulkIn devices such as digital still cameras and image scanners. In addition, Mass Storage devices are also applicable to this device.

# FEATURES

- USB 1.0 compliant

- Built-in USB transceiver circuit

- Full-speed (12 Mb/sec) support

- Supports printer device class, image device class, and Mass Storage device class

- Supports three types of transfer; control transfer, bulk transfer, and interrupt transfer

- Built-in FIFOs for control transfer Two 8-byte FIFOs (one for receive FIFO and the other for transmit FIFO)

- Built-in FIFOs for bulk transfer (available for either receive FIFO or transmit FIFO) One 64-byte FIFO Two 64-byte FIFOs

- Built-in FIFO for interrupt transfer One 8-byte FIFO

- Supports one control endpoint, two bulk endpoint addresses, and one interrupt endpoint address

- Two 64-byte FIFOs enable fast BulkOut transfer and BulkIn transfer

- Supports 8 bit/16 bit DMA transfer

- V<sub>CC</sub> is 3.0 V to 3.6 V

- Supporting dual power supply enables 5 V application interface

- Built-in 48 MHz oscillator circuit

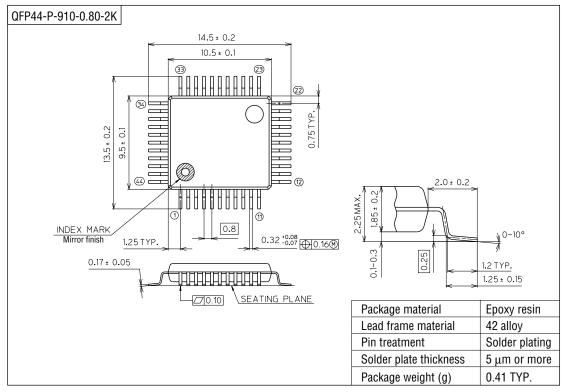

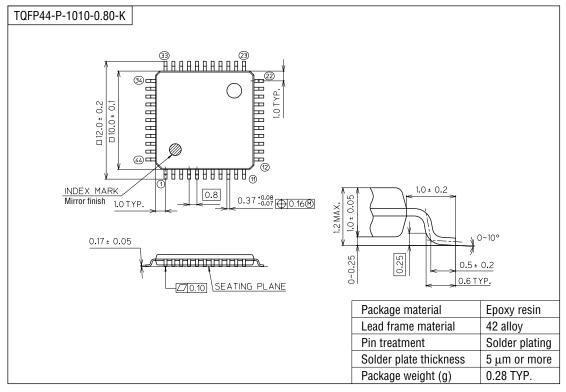

- Package options: 44-pin plastic QFP (QFP44-P-910-0.80-2K) (Product name: ML60851AGA) 44-pin plastic TQFP (TQFP44-P-1010-0.80-K) (Product name: ML60851ATB)

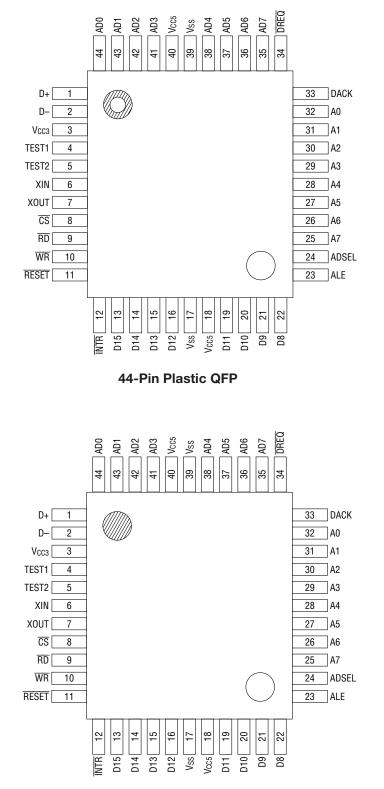

# **PIN CONFIGURATION (TOP VIEW)**

44-Pin Plastic TQFP

# **PIN DESCRIPTION**

| Pin                   | Symbol    | Туре | Description                                                      |

|-----------------------|-----------|------|------------------------------------------------------------------|

| 1, 2                  | D+, D–    | I/0  | USB data                                                         |

| 6, 7                  | XIN, XOUT | —    | Pin for external crystal oscillator                              |

| 4, 5                  | TEST1, 2  | I    | Test Pins (normally "L")                                         |

| 13 to 16,<br>19 to 22 | D15:D8    | I/0  | Data bus (MSB)                                                   |

| 35 to 38,<br>41 to 44 | AD7:AD0   | I/0  | Data bus (LSB)/address input                                     |

| 25 to 32              | A7:A0     | I    | Address input                                                    |

| 8                     | CS        | I    | Chip select signal input pin. LOW active                         |

| 9                     | RD        | I    | Read signal input pin. LOW active                                |

| 10                    | WR        | I    | Write signal input pin. LOW active                               |

| 12                    | INTR      | 0    | Interrupt request signal output pin                              |

| 34                    | DREQ      | 0    | DMA request output pin                                           |

| 33                    | DACK      | I    | DMA acknowledge signal input pin                                 |

| 23                    | ALE       | I    | Address latch enable signal input pin                            |

| 24                    | ADSEL     | I    | Address input mode select input pin. "H": address/data multiplex |

| 11                    | RESET     | I    | System Reset signal input pin. LOW active                        |

# **INTERNAL REGISTERS**

# Addresses and Names of Registers

|       | Address |        |                                        |  |

|-------|---------|--------|----------------------------------------|--|

| A5:A0 | Read    | Write  | Register name                          |  |

| A5:AU | A7, A6  | A7, A6 |                                        |  |

| 00h   | 11b     | 01b    | Device Address Register                |  |

| 01h   | 11b     | 01b    | Device State Register                  |  |

| 02h   | 11b     |        | Packet Error Register                  |  |

| 03h   | 11b     | —      | Receive FIFO Register                  |  |

| 04h   | 11b     |        | Transmit FIFO Register                 |  |

| 08h   | 11b     | 01b    | Endpoint Packet-Ready Register         |  |

| 09h   | 11b     |        | Endpoint 0 Receive-Byte Count Register |  |

| 0Ah   | 11b     |        | Endpoint 1 Receive-Byte Count Register |  |

| 0Bh   | 11b     |        | Endpoint 2 Receive-Byte Count Register |  |

| 0Eh   |         | 01b    | Flash Transmit FIFO                    |  |

| 0Fh   | —       | 01b    | System Control                         |  |

| 10h   | 11b     |        | bmRequestType Setup Register           |  |

| 11h   | 11b     |        | bRequest Setup Register                |  |

| 12h   | 11b     | —      | wValue LSB Setup Register              |  |

| 13h   | 11b     |        | wValue MSB Setup Register              |  |

| 14h   | 11b     |        | wIndex LSB Setup Register              |  |

| 15h   | 11b     | —      | wIndex MSB Setup Register              |  |

| 16h   | 11b     | —      | wLength LSB Setup Register             |  |

| 17h   | 11b     | —      | wLength MSB Setup Register             |  |

| 1Ah   | 11b     | 01b    | Assertion Select Register              |  |

| 1Bh   | 11b     | 01b    | Interrupt Enable Register              |  |

| 1Ch   | 11b     | _      | Interrupt Status Register              |  |

| 1Dh   | 11b     | 01b    | DMA Control Register                   |  |

| 1Eh   | 11b     | 01b    | DMA Interval Register                  |  |

| 1Fh   | _       |        | Reserved                               |  |

| 20h   | 11b     |        | Endpoint 0 Receive Control Register    |  |

| 21h   | 11b     |        | Endpoint 0 Receive General Register    |  |

| 22h   | 11b     | 01b    | Endpoint 0 Receive Payload Register    |  |

| 23h   |         |        | Reserved                               |  |

| 24h   | 11b     | 01b    | Endpoint 1 Control Register            |  |

| 25h   | 11b     | 01b    | Endpoint 1 General Register            |  |

| 26h   | 11b     | 01b    | Endpoint 1 Payload Register            |  |

| 27h   |         |        | Reserved                               |  |

# Addresses and Names of Registers (Continued)

|       | Address |        |                                      |

|-------|---------|--------|--------------------------------------|

| A5:A0 | Read    | Write  | Register name                        |

| A5:AU | A7, A6  | A7, A6 |                                      |

| 30h   | 11b     |        | Endpoint 0 Transmit Control Register |

| 31h   | 11b     |        | Endpoint 0 Transmit General Register |

| 32h   | 11b     | 01b    | Endpoint 0 Transmit Payload Register |

| 33h   | 11b     | 01b    | Endpoint 0 General Register          |

| 34h   | 11b     | 01b    | Endpoint 2 Control Register          |

| 35h   | 11b     | 01b    | Endpoint 2 General Register          |

| 36h   | 11b     | 01b    | Endpoint 2 Payload Register          |

| 37h   |         | —      | Reserved                             |

| 38h   | 11b     | 01b    | Endpoint 3 Control Register          |

| 39h   | 11b     | 01b    | Endpoint 3 General Register          |

| 3Ah   | 11b     | 01b    | Endpoint 3 Payload Register          |

| 00h   | 01b     | —      | Endpoint 0 Receive FIFO data         |

| 01h   | 01b     | —      | Endpoint 1 Receive FIFO data         |

| 02h   | 01b     |        | Endpoint 2 Receive FIFO data         |

| 00h   |         | 11b    | Endpoint 0 Transmit FIFO data        |

| 01h   | _       | 11b    | Endpoint 1 Transmit FIFO data        |

| 02h   | —       | 11b    | Endpoint 2 Transmit FIFO data        |

| 03h   |         | 11b    | Endpoint 3 Transmit FIFO data        |

#### **Register Description**

Device Address Register (C0h, 40h)

| D7  | D6 | D5 | D4 | D3             | D2   | D1 | D0 |

|-----|----|----|----|----------------|------|----|----|

| RFU |    |    | De | vice Address ( | R/W) |    |    |

The local MCU writes a device address, which is given by the SET\_ADDRESS command form the host computer, into this register. Thereafter, this device processes an only token packet transmitted to the given device address.

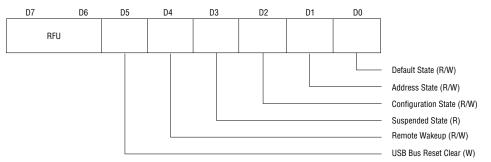

Device State Register (C1h, 41h)

Default, Address, and Configuration States: D2, D1, and D0 are set to 0, 0, and 1 (default states) by reset respectively. Changing the values of this register gives no influence on operation of this device.

Suspended State: This register is asserted when the device enters the suspended state. This register is deaserted by reset or when the device exits the suspended state by a resume signaling from the USB bus.

Remote Wakeup: When this device signals a remote wakeup during the suspended state, this register is asserted by a local MCU. This register is automatically deasserted when the device exits the suspended state by a resume signaling from the USB bus.

USB Bus Reset Status Clear: Writing "1" to this bit causes the interrupt status to be cleared (the USB bus reset interrupt status bit is "0" and the INTR pin is deasserted) while the USB bus reset interrupt is being serviced (when D5, the USB bus reset interrupt status bit, of the interrupt status register is "1" and the INTR pin is asserted). This bit is readable, and when read, its value will be always "0".

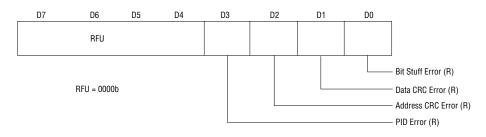

Packet Error Register (C2h, –)

#### FIFO Status Register 1 (C3h, –) D5 D7 D6 D4 D3 D2 D1 D0 RFU Receive FIF00 Full (R) RFU = 0000bReceive FIFO0 Empty (R) FIF01 Full (R) FIF01 Empty (R) FIFO Status Register 2 (C4h, –) D7 D6 D5 D4 D3 D2 D1 D0 RFU Transmit FIF00 Full (R) Transmit FIF00 Empty (R) FIF02 Full (R) RFU = 0000b FIF02 Empty (R) FIF03 Full (R) FIF03 Empty (R)

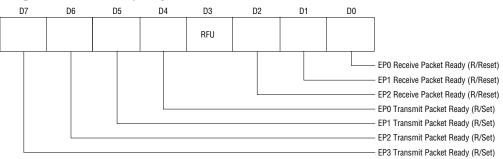

#### Endpoint Packet-Ready Register (C8h, 48h)

Receive Packet Ready: When a valid packet arrives at an endpoint, this bit is automatically set and the endpoint is locked. When "1" is written in this register, Receiver Packet Ready is reset and the endpoint is unlocked. (This bit also is set to "0".)

When DMA is enabled, EP1 Receive Packet Ready is automatically reset after all the data in EP1 is read during DMA transfer.

Transmit Packet Ready: When "1" is written in this register, the Transmit Packet Ready is set and the packet in the corresponding endpoint is transmitted. Transmit Packet Ready is automatically reset when the ACK handshake is returned from the host.

When DMA is enabled, EP1 Transmit Packet Ready is automatically set after the data written in EP1 reaches the maximum packet size during DMA transfer.

The value of this register remains unchanged when "0" is written in this register.

#### Endpoint 0 Receive Byte Count Register (C9h, -)

| D7  | D6 | D5                 | D4 | D3 | D2 | D1 | D0 |  |

|-----|----|--------------------|----|----|----|----|----|--|

| RFU |    | EPO Byte Count (R) |    |    |    |    |    |  |

|     |    |                    |    |    |    |    |    |  |

#### Endpoint 1 Receive Byte Count Register (CAh, -)

| D7  | D6 | D5 | D4 | D3            | D2  | D1 | D0 |

|-----|----|----|----|---------------|-----|----|----|

| RFU |    |    | E  | P1 Byte Count | (R) |    |    |

#### Endpoint 2 Receive Byte Count Register (CBh, -)

| D7  | D6 | D5 | D4 | D3            | D2    | D1 | D0 |

|-----|----|----|----|---------------|-------|----|----|

| RFU |    |    | E  | P2 Byte Count | t (R) |    |    |

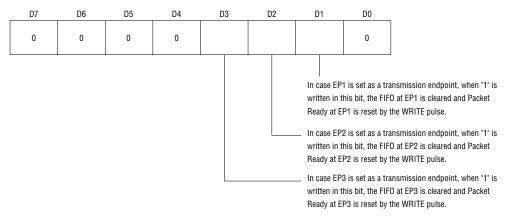

#### Flash Transmit FIFO (-, 4Eh)

#### Note: Please clear all FIFOs at the same time, otherwise some of them may not be cleared.

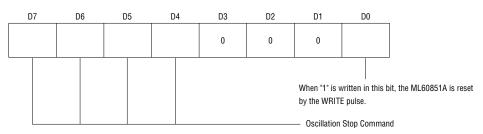

#### System Control (-, 4Fh)

Oscillation Stop Command: Writing 1010b to D7 to D4, (writing A0h into this register) causes the oscillator circuit of the ML60851A to be deactivated and go into the standby mode.

When oscillation is stopped, reading and writing into the register is possible but reading and writing into FIFO is not possible. Asserting the RESET pin restarts oscillation.

#### bmRequestType Setup Register (D0h, -)

| D7 | D6       | D5          | D4               | D3            | D2 | D1 | D0                                                                              |

|----|----------|-------------|------------------|---------------|----|----|---------------------------------------------------------------------------------|

|    | Type (R) |             |                  | Recipient (R) |    |    |                                                                                 |

|    |          |             |                  |               |    |    | 0 = Device<br>1 = Interface<br>2 = Endpoint<br>3 = Others<br>4 to 31 = Reserved |

|    |          |             |                  |               |    |    | 0 = Standard<br>1 = Class<br>2 = Vendor<br>3 = Reserved                         |

|    |          | —— Data Tra | ansfer Direction | (R)           |    |    | 0 = Host to device<br>1 = Device to host                                        |

#### bRequest Setup Register (D1h, -)

| D7 | D6                   | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

|----|----------------------|----|----|----|----|----|----|--|--|--|

|    | Specific Request (R) |    |    |    |    |    |    |  |  |  |

|    |                      |    |    |    |    |    |    |  |  |  |

- wValueLSB Setup Register (D2h, –) D7:D0 = LSB of Word Size Field (R)

- wValueMSB Setup Register (D3h, –) D7:D0 = MSB of Word Size Field (R)

- wIndexLSB Setup Register (D4h, –) D7:D0 = LSB of Word Size Field (R)

- wIndexMSB Setup Register (D5h, –) D7:D0 = MSB of Word Size Field (R)

- wLengthLSB Setup Register (D6h, –) This field defines the length of data that is transferred in the second stage (data stage) of control transfer. (R)

- wLengthMSB Setup Register (D7h, –) This field defines the length of data that is transferred in the data stage of control transfer. (R)

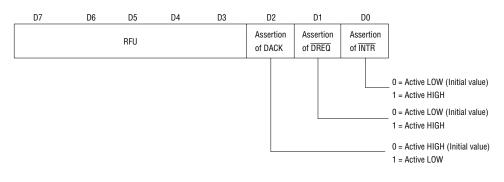

#### Assertion Select Register (DAh, 5Ah) (R/W)

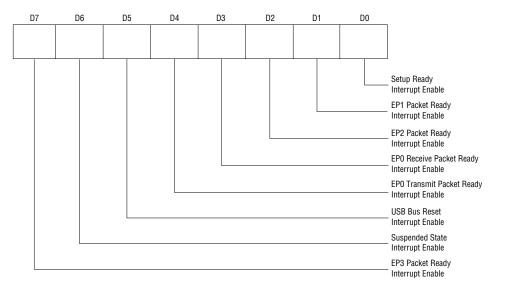

#### Interrupt Enable Register (DBh, 5Bh) (R/W)

Initial value of D0 is 1. Initial values of D1 to D7 are 0.

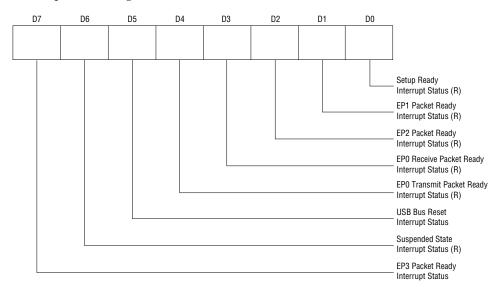

Interrupt Status Register (DCh, 5Ch) (R)

Setup Ready Interrupt Status: Equivalent to Setup Ready at (F3h) described later when the corresponding Interrupt Enable bit is asserted.

EP1 Packet Ready Interrupt Status: Equivalent to EP1 Receive Packet Ready (the complement of EP1 Transmit Packet Ready when EP1 is set for transmitter) at (C8h) described before when the corresponding Interrupt Enable bit is asserted.

EP2 Packet Ready Interrupt Status: Equivalent to EP2 Receive Packet Ready (the complement of EP2 Transmit Packet Ready when EP2 is set for transmitter) at (C8h) described before when the corresponding Interrupt Enable bit is asserted.

EP0 Receive Packet Ready Interrupt Status: Equivalent to EP0 Receive Packet Ready at (C8h) described before when the corresponding Interrupt Enable bit is asserted.

EP0 Transmit Packet Ready Interrupt Status: Equivalent to the complement of EP0 Transmit Packet Ready at (C8h) described before when the corresponding Interrupt Enable bit is asserted.

USB Bus Reset Interrupt Status: This bit is set to "1" at USB bus reset when the D5 bit of the interrupt enable register (DBh) is "1". To return this bit back to "0", "1" should be written to the D5 bit of the device states register.

Suspended State Interrupt Status: Equivalent to Suspended State Register at (C1h) described before when the corresponding Interrupt Enable bit is asserted.

EP3 Packet Ready Interrupt Status: When the D7 bit of the interrupt enable register (DBh) is "1", the complement of the D7 bit of the endpoint packet ready register (C8h) is being copied.

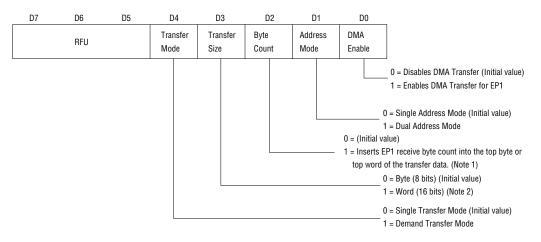

#### DMA Control Register (DDh, 5Dh) (R/W)

- (Note 1) When 16-bit mode is set, the upper byte of the top word is 00h.

- (Note 2) When 16-bit mode is set and the packet size is an odd-number byte, the upper byte of the last word is 00h.

DMA Interval Register (DEh, 5Eh) (R/W)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |

This register specifies a DMA transfer interval between de-assertion and re-assertion of DREQ in Single Transfer mode. The interval is specified between 0 and 255 (bit times). The initial value is 0.

1-bit time = 1/12 MHz (= 84 ns)

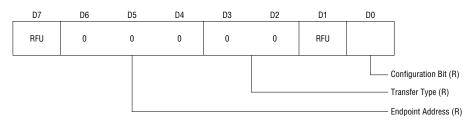

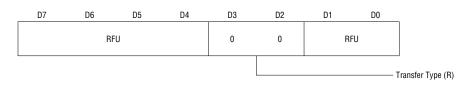

#### Endpoint 0 Receive Control Register (E0h, -)

Configuration Bit: Only when this bit is asserted ("1"), a packet transmitted from a host computer to this EP is received. The packet is ignored when this bit is deasserted ("0"). This bit is deasserted by system reset and is asserted by USB reset (both D+ and D- are 0s for more than  $2.5 \,\mu$ s).

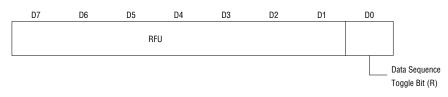

Endpoint 0 Receive General Register (E1h, -)

Endpoint 0 Receive Payload Register (E2h, 62h)

| D7  | D6                        | D5 | D4 | D3 | D2   | D1 | D0 |  |  |

|-----|---------------------------|----|----|----|------|----|----|--|--|

| RFU | Maximum Packet Size (R/W) |    |    |    |      |    |    |  |  |

|     |                           |    |    |    | - () |    |    |  |  |

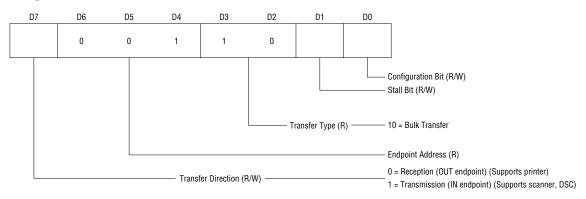

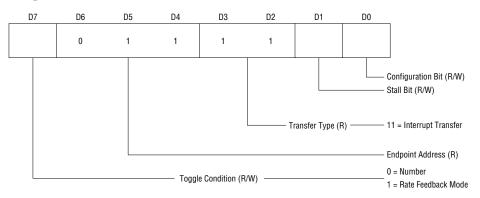

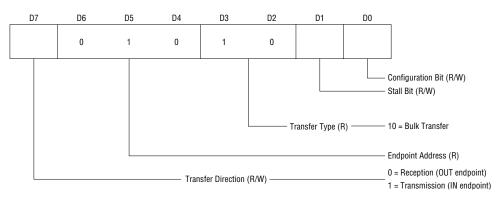

Endpoint 1 Control Register (E4h, 64h)

Register to set the attribute of EP1.

To use EP1, the local MCU writes EP1's attribute in this register by the request from the host computer.

Configuration Bit: Only when this bit is asserted ("1"), a packet transmitted from the host computer to this EP is received. The packet is ignored when this bit is deasserted ("0"). Whether or not this EP is configured can be known by referencing this bit.

Stall Bit: When this bit is asserted ("1"), a stall handshake for a packet transmitted from the host computer to this EP is automatically returned to the host computer.

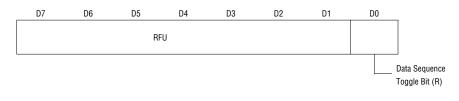

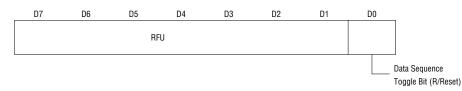

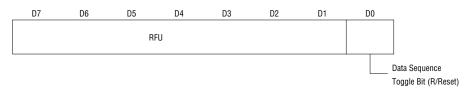

Endpoint 1 General Register (E5h, 65h)

Data Sequence Toggle Bit: When initializing EP, PID of DATA0 is specified after resetting the Data Packet Toggle bit by writing "1" to this bit (this bit goes to "0").

Endpoint 1 Payload Register (E6h, 66h)

Endpoint 3 Control Register (F8h, 78h)

Register to set the attribute of EP3.

To use EP3, the local MCU writes EP3's attribute in this register by the request from the host computer.

Configuration Bit: Only when this bit is asserted ("1"), a packet transmitted from the host computer to this EP is received. The packet is ignored when this bit is deasserted ("0"). Whether or not this EP is configured can be known by referencing this bit.

Stall Bit: When this bit is asserted ("1"), a stall handshake for a packet transmitted from the host computer to this EP is automatically returned to the host computer.

Toggle Condition Bit: When this bit is "0", DATA0 and DATA1 are toggled each time ACK is received form the host computer by the EP3. Setting this bit to "1" causes the ML60851A to go into the rate feedback mode, in which case DATA0 and DATA1 are toggled each time the packet ready is asserted by the local MCU.

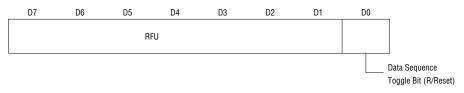

Endpoint 3 General Register (F9h, 79h)

Data Sequence Toggle Bit: When initializing EP, PID of DATA0 is specified after resetting the Data Packet Toggle bit by writing "1" to this bit (this bit goes to "0").

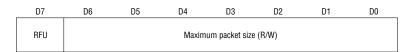

Endpoint 3 Payload Register (FAh, 7Ah)

| D7  | D6 | D5 | D4    | D3              | D2      | D1 | D0 |

|-----|----|----|-------|-----------------|---------|----|----|

| RFU |    |    | Maxim | ium packet size | e (R/W) |    |    |

#### Endpoint 0 Transmit Control Register (F0h, -)

#### Endpoint 0 Transmit General Register (F1h, -)

#### Endpoint 0 Transmit Payload Register (F2h, 72h)

| D7  | D6 | D5 | D4    | D3            | D2      | D1 | D0 |

|-----|----|----|-------|---------------|---------|----|----|

| RFU |    |    | Maxim | um Packet Siz | e (R/W) |    |    |

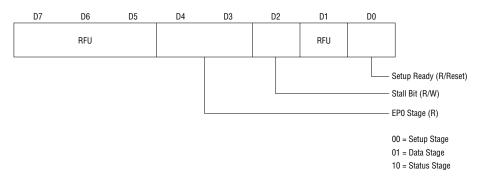

#### Endpoint 0 Transmit General Register (F3h, 73h)

Setup Ready: When a valid setup packet has arrived at an 8-byte setup register, this register is automatically set and the receive FIFO at endpoint 0 is locked. Writing "1" in this register resets Setup Ready. When the data stage of Control Write transaction follows, Packet Ready at endpoint 0 is also reset. Therefore, the endpoint 0 receive FIFO is unlocked and ready to receive the packets in the data stage.

The value of this register remains unchanged when "0" is written in this register.

#### Endpoint 2 Control Register (F4h, 74h)

Configuration Bit: Only when this bit is asserted ("1"), a packet transmitted from the host computer to this EP is received. The packet is ignored when this bit is deasserted ("0"). Whether or not this EP is configured can be known by referencing this bit.

Stall Bit: When this bit is asserted ("1"), a stall handshake for a packet transmitted from the host computer to this EP is automatically returned to the host computer.

Endpoint 2 General Register (F5h, 75h)

Data Sequence Toggle Bit: When initializing EP, PID of DATA0 is specified after resetting the Data Packet Toggle bit by writing "1" to this bit (this bit goes to "0").

Endpoint 2 Payload Register (F6h, 76h)

| D7  | D6 | D5 | D4    | D3            | D2      | D1 | D0 |

|-----|----|----|-------|---------------|---------|----|----|

| RFU |    |    | Maxim | um Packet Siz | e (R/W) |    |    |

Endpoint 0 Receive FIFO Data (40h, -)

| D7 | D6 | D5   | D4          | D3           | D2    | D1 | D0 |

|----|----|------|-------------|--------------|-------|----|----|

|    |    | Endp | oint 0 Rece | ive FIFO Dat | a (R) |    |    |

Area to store data to be transmitted from the host computer to this device in the data stage of Control Write transfer.

Endpoint 1 Receive FIFO Data (41h, -)

| D7 | D6 | D5   | D4          | D3           | D2    | D1 | D0 |

|----|----|------|-------------|--------------|-------|----|----|

|    |    | Endp | oint 1 Rece | ive FIFO Dat | a (R) |    |    |

Area to store data to be transmitted from the host computer to EP1 of this device in Bulk Out transfer. This register is valid only when EP1 is set for the OUT endpoint.

Endpoint 2 Receive FIFO Data (42h, -)

| D7 | D6 | D5   | D4          | D3           | D2    | D1 | D0 |

|----|----|------|-------------|--------------|-------|----|----|

|    |    | Endp | oint 2 Rece | ive FIFO Dat | a (R) |    |    |

Area to store data to be transmitted from the host computer to EP2 of this device in Bulk Out transfer. This register is valid only when EP2 is set for the OUT endpoint.

Endpoint 0 Transmit FIFO Data (-, C0h)

| D7 | D6 | D5    | D4            | D3           | D2    | D1 | D0 |

|----|----|-------|---------------|--------------|-------|----|----|

|    |    | Endpo | oint 0 Transi | mit FIFO Dat | a (W) |    |    |

Area to store data to be transmitted from this device to the host computer in the data stage of Control Read transter.

Endpoint 1 Transmit FIFO Data (-, C1h)

| D7 | D6 | D5    | D4           | D3           | D2     | D1 | D0 |

|----|----|-------|--------------|--------------|--------|----|----|

|    |    | Endpo | oint 1 Trans | mit FIFO Dat | ta (W) |    |    |

Area to store data to be transmitted from EP1 of this device to the host computer in Bulk In transfer. This register is valid only when EP1 is set for the IN endpoint.

Endpoint 2 Transmit FIFO Data (-, C2h)

| D7 | D6 | D5    | D4            | D3           | D2    | D1 | D0 |

|----|----|-------|---------------|--------------|-------|----|----|

|    |    | Endpo | oint 2 Transı | mit FIFO Dat | a (W) |    |    |

Area to store data to be transmitted from EP2 of this device to the host computer in Bulk In transfer. This register is valid only when EP2 is set for the IN endpoint.

Endpoint 3 Transmit FIFO Data (-, C3h)

| D7 | D6 | D5    | D4           | D3           | D2     | D1 | D0 |

|----|----|-------|--------------|--------------|--------|----|----|

|    |    | Endpo | oint 3 Trans | mit FIFO Dat | ta (W) |    |    |

Area to store data to be transmitted from EP3 of this device to the host computer in Bulk In transfer. This register is valid only when EP3 is set for the IN endpoint.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition | Rating                         | Unit |

|---------------------|------------------|-----------|--------------------------------|------|

| Power Supply 3      | V <sub>CC3</sub> | —         | -0.3 to +4.6                   | V    |

| Power Supply 5      | V <sub>CC5</sub> | —         | -0.5 to +6.5                   | V    |

| Input Voltage       | VI               | _         | -0.3 to V <sub>CC5</sub> + 0.3 | V    |

| Storage Temperature | T <sub>STG</sub> | _         | -55 to +150                    | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol           | Condition | Range      | Unit |

|-----------------------|------------------|-----------|------------|------|

| Power Supply 3        | V <sub>CC3</sub> | —         | 3.0 to 3.6 | V    |

| Power Supply 5        | V <sub>CC5</sub> | —         | 3.0 to 5.5 | V    |

| Operating Temperature | Та               | —         | 0 to 70    | °C   |

| Oscillation Frequency | F <sub>OSC</sub> | —         | 48         | MHz  |

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics (1)**

| Parameter                   | Symbol            | Condition                 | Min.                | Тур.  | Max.                   | Unit | Applicable pin   |  |

|-----------------------------|-------------------|---------------------------|---------------------|-------|------------------------|------|------------------|--|

| High-level Input<br>Voltage | V <sub>IH</sub>   | _                         | 2.0                 | _     | V <sub>CC5</sub> + 0.3 | V    |                  |  |

| Low-level Input<br>Voltage  | VIL               | _                         | -0.3                | _     | +0.8                   | V    | - Note 1         |  |

| High-level Input<br>Voltage | V <sub>IH</sub>   | —                         | $V_{CC3} 	imes 0.8$ | —     | V <sub>CC3</sub> + 0.3 | V    | – XIN            |  |

| Low-level Input<br>Voltage  | V <sub>IL</sub>   | _                         | -0.3                | —     | $V_{CC3}\!\times\!0.2$ | V    |                  |  |

| Cobmitt Triggor             | V <sub>t+</sub>   | —                         | —                   | 1.6   | 2.0                    | V    |                  |  |

| Schmitt Trigger             | V <sub>t</sub> -  | —                         | 0.8                 | 1.2   | —                      | V    | RESET            |  |

| Input Voltage               | $\Delta V_t$      | $(V_{t+}) - (V_{t-})$     | 0.1                 | 0.4   | —                      | V    |                  |  |

| High-level                  | N.                | I <sub>OH</sub> = −100 μA | $V_{CC5} - 0.2$     |       | —                      | V    | D1C-D0           |  |

| Output Voltage              | V <sub>OH</sub>   | I <sub>OH</sub> =4 mA     | 2.4                 |       | —                      | V    | D15:D8           |  |

| Low-level                   | Ma                | I <sub>0L</sub> = 100 μA  | —                   |       | 0.2                    | V    | AD7:AD0          |  |

| Output Voltage              | V <sub>OL</sub>   | $I_{OL} = 4 \text{ mA}$   | —                   |       | 0.4                    | V    | INTR, DREQ       |  |

| High-level Input<br>Current | IIH               | $V_{IH} = V_{CC5}$        | _                   | 0.01  | 1                      | μA   | – Note 2         |  |

| Low-level Input<br>Current  | IIL               | $V_{IL} = V_{SS}$         | -1                  | -0.01 | _                      | μΑ   | NULE 2           |  |

| 3-state Output              | I <sub>OZH</sub>  | $V_{OH} = V_{CC5}$        | —                   | 0.01  | 1                      | μA   | D15:D8           |  |

| Leakage Current             | I <sub>OZL</sub>  | $V_{OL} = V_{SS}$         | -1                  | -0.01 | —                      | μA   | AD7:AD0          |  |

| Power Supply                | I <sub>CC3</sub>  | —                         | —                   | —     | 50                     | mA   | V <sub>CC3</sub> |  |

| Current (Operating)         | I <sub>CC5</sub>  |                           | —                   | _     | 5                      | mA   | V <sub>CC5</sub> |  |

| Power Supply                | I <sub>CCS3</sub> | Note 3                    | _                   | _     | 50                     | μA   | V <sub>CC3</sub> |  |

| Current (Standby)           | I <sub>CCS5</sub> | Note 3                    | _                   | _     | 50                     | μA   | V <sub>CC5</sub> |  |

Notes: 1. Applied to D15:D8, AD7:AD0, A7:A0, CS, RD, WR, DACK, ALE, and ADSEL.

2. Applied to XIN, A7:A0,  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , DACK, ALE, and ADSEL.  $V_{IH} = V_{CC3}$  for only XIN.

3. The XIN pin is fixed to High level or Low level in the suspend state. All the output pins are open.

|                             |                   | (V <sub>C</sub>           | <sub>C5</sub> = 4.5 to 5. | 5 V, V <sub>CC3</sub> = 3 | 3.0 to 3.6 V, V        | / <sub>SS</sub> = 0 V, | Ta = 0 to 70°C)  |

|-----------------------------|-------------------|---------------------------|---------------------------|---------------------------|------------------------|------------------------|------------------|

| Parameter                   | Symbol            | Condition                 | Min.                      | Тур.                      | Max.                   | Unit                   | Applicable pin   |

| High-level Input<br>Voltage | V <sub>IH</sub>   | _                         | 2.2                       | —                         | V <sub>CC5</sub> + 0.5 | V                      | - Note 1         |

| Low-level Input<br>Voltage  | V <sub>IL</sub>   | —                         | -0.5                      | —                         | +0.8                   | V                      | NOLE I           |

| Schmitt Trigger             | V <sub>t+</sub>   | —                         |                           | 1.7                       | 2.2                    | V                      |                  |

| Input Voltage               | V <sub>t</sub> -  | —                         | 0.8                       | 1.4                       | —                      | V                      | RESET            |

| mput vonage                 | $\Delta V_t$      | $(V_{t+}) - (V_{t-})$     | 0.2                       | 0.3                       | _                      | V                      |                  |

| High-level                  | Val               | I <sub>0H</sub> = −100 μA | $V_{CC5} - 0.2$           | —                         | —                      | V                      | D15:D8           |

| Output Voltage              | V <sub>OH</sub>   | $I_{OH} = -8 \text{ mA}$  | 3.7                       | —                         |                        | V                      | - AD7:AD0        |

| Low-level                   | Va                | l <sub>0L</sub> = 100 μA  |                           | —                         | 0.2                    | V                      | INTR, DREQ       |

| Output Voltage              | V <sub>OL</sub>   | I <sub>0L</sub> = 8 mA    |                           | —                         | 0.4                    | V                      | INTR, DREQ       |

| High-level Input<br>Current | I <sub>IH</sub>   | $V_{IH} = V_{CC5}$        |                           | 0.01                      | 10                     | μA                     | Note 2           |

| Low-level Input<br>Current  | IL                | $V_{IL} = V_{SS}$         | -10                       | -0.01                     | _                      | μA                     | NOLE 2           |

| 3-state Output              | I <sub>OZH</sub>  | $V_{OH} = V_{CC5}$        |                           | 0.01                      | 10                     | μΑ                     | D15:D8           |

| Leakage Current             | I <sub>OZL</sub>  | $V_{OL} = V_{SS}$         | -10                       | -0.01                     | _                      | μA                     | AD7:AD0          |

| Power Supply                | I <sub>CC3</sub>  |                           | —                         |                           | 50                     | mA                     | V <sub>CC3</sub> |

| Current (Operating)         | I <sub>CC5</sub>  |                           | —                         | —                         | 5                      | mA                     | V <sub>CC5</sub> |

| Power Supply                | I <sub>CCS3</sub> | Note 3                    |                           | —                         | 50                     | μA                     | V <sub>CC3</sub> |

| Current (Standby)           | I <sub>CCS5</sub> | Note 3                    |                           |                           | 50                     | μA                     | V <sub>CC5</sub> |

#### DC Characteristics (2)

Notes: 1. Applied to D15:D8, AD7:AD0, A7:A0,  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , DACK, ALE, and ADSEL. The DC characteristics (1) applies to XIN.

2. Applied to A7:A0,  $\overrightarrow{CS}$ ,  $\overrightarrow{RD}$ ,  $\overrightarrow{WR}$ , DACK, ALE, and ADSEL. The DC characteristics (1) applies to XIN.

3. The XIN pin is fixed to High level or Low level in the suspend state. All the output pins are open.

|                     |                 |                                        |      | $(V_{CC3} = 3)$ | .0 to 3.6 V, \ | $V_{\rm SS} = 0  \rm V,$ | $Ta = 0 \text{ to } 70^{\circ}\text{C})$ |

|---------------------|-----------------|----------------------------------------|------|-----------------|----------------|--------------------------|------------------------------------------|

| Parameter           | Symbol          | Condition                              | Min. | Тур.            | Max.           | Unit                     | Applicable pin                           |

| Differential Input  | V               |                                        | 0.2  |                 |                | v                        |                                          |

| Sensitivity         | V <sub>DI</sub> | (D+) - (D-)                            | 0.2  |                 |                | v                        |                                          |

| Differential Common | V               | Includes V renge                       | 0.0  |                 | 0.5            | v                        |                                          |

| Mode Range          | V <sub>CM</sub> | Includes V <sub>DI</sub> range         | 0.8  |                 | 2.5            | V                        |                                          |

| Single Ended        | M               |                                        | 0.0  |                 | 0.0            | V                        |                                          |

| Receiver Threshold  | V <sub>SE</sub> |                                        | 0.8  |                 | 2.0            | V                        | D. D                                     |

| High-level Output   | V               |                                        | 2.8  |                 | 2.6            | v                        | D+, D-                                   |

| Voltage             | V <sub>OH</sub> | RL of 15 k $\Omega$ to V <sub>SS</sub> | 2.0  |                 | 3.6            | v                        |                                          |

| Low-level Output    | V               |                                        |      |                 | 0.0            | v                        |                                          |

| Voltage             | V <sub>OL</sub> | RL of 1.5 kΩ to 3.6 V                  |      |                 | 0.3            | v                        |                                          |

| Output Leakage      | 1.              | 0 1/ 2 1/ 2 2 1/                       | -10  |                 | +10            |                          |                                          |

| Current             | ILO             | 0 V < V <sub>IN</sub> < 3.3 V          | -10  |                 | +10            | μA                       |                                          |

#### **DC** Characteristics (3) USB Port

Δ. 2.0 to 2.6 V/ V. . . 0.V/ To . . 0 to 70°C

# **AC Characteristics USB Port**

$(V_{CC3} = 3.0 \text{ to } 3.6 \text{ V}, V_{SS} = 0 \text{ V}, \text{ Ta} = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                          | Symbol             | Condition<br>(Notes 1. and 2.)    | Min.  | Тур. | Max.  | Unit | Applicable pin |

|------------------------------------|--------------------|-----------------------------------|-------|------|-------|------|----------------|

| Rise Transition Time               | t <sub>R</sub>     | CL = 50 pF                        | 4     |      | 25    | ns   |                |

| Fall Transition Time               | t <sub>F</sub>     | CL = 50 pF                        | 4     |      | 25    | ns   |                |

| Rise/Fall Time<br>Matching         | t <sub>RFM</sub>   | (t <sub>R</sub> /t <sub>F</sub> ) | 90    |      | 140   | %    | _              |

| Output Signal<br>Crossover Voltage | V <sub>CRS</sub>   |                                   | 1.2   |      | 2     | V    | D+, D-         |

| Driver Output<br>Resistance        | Z <sub>DRV</sub>   | Steady State Driver               | 28    |      | 43    | Ω    | _              |

| Data Rate                          | t <sub>DRATE</sub> | Ava. Bit<br>Rate (12 Mb/s ±0.25%) | 11.97 |      | 12.03 | Mbs  |                |

Notes: 1.  $1.5 \text{ k}\Omega$  pull-up to 2.8 V on the D+ data line.

2. Measured from 10% to 90% of the data signal.

#### TIMING DIAGRAM

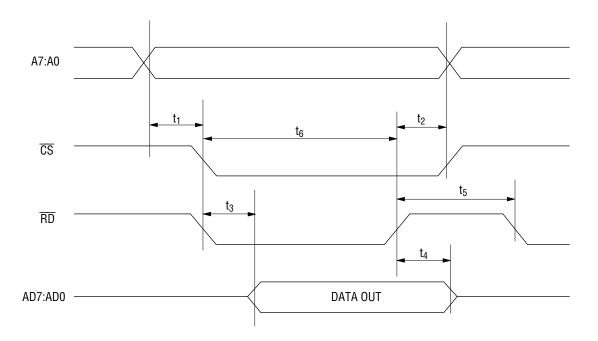

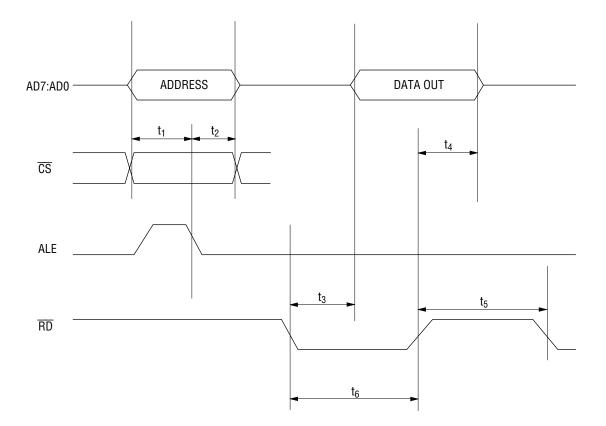

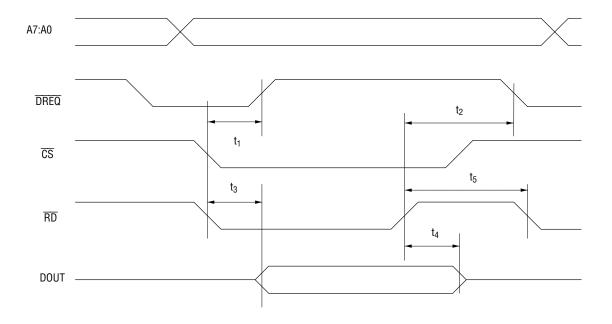

#### READ Timing (1) (Address Separate ADSEL = 0)

| Parameter               | Symbol                  | Condition  | Min. | Max. | Unit | Note |

|-------------------------|-------------------------|------------|------|------|------|------|

| Address Setup Time (RD) | t <sub>1</sub> (RD)     |            | 21   |      | ns   | 5    |

| Address Setup Time (CS) | $t_1 \ (\overline{CS})$ |            | 10   |      | ns   | 5    |

| Address (CS) Hold Time  | t <sub>2</sub>          |            | 0    | —    | ns   | 2    |

| Read Data Delay Time    | t <sub>3</sub>          | Load 20 pF | —    | 25   | ns   | 1    |

| Read Data Hold Time     | t4                      |            | 0    |      | ns   |      |

| Recovery Time           | t <sub>5</sub>          | FIFO READ  | 63   |      | ns   | 3    |

| FIFO Access Time        | t <sub>6</sub>          | FIFO READ  | 42   |      | ns   | 4    |

Notes: 1.  $t_1$  and  $t_3$  are defined depending upon  $\overline{CS}$  or  $\overline{RD}$  which becomes active last.

2.  $t_2$  is defined depending upon  $\overline{CS}$  or  $\overline{RD}$  which becomes active first.

3. 3-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

- 4. 2-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

- 5. Either of them should be met.

| Parameter               | Symbol         | Condition  | Min. | Max. | Unit | Note |

|-------------------------|----------------|------------|------|------|------|------|

| Address (CS) Setup Time | t1             |            | 10   |      | ns   |      |

| Address (CS) Hold Time  | t <sub>2</sub> |            | 0    |      | ns   |      |

| Read Data Delay Time    | t3             | Load 20 pF | _    | 25   | ns   |      |

| Read Data Hold Time     | t4             |            | 0    | —    | ns   |      |

| Recovery Time           | t <sub>5</sub> | FIFO READ  | 63   | _    | ns   | 1    |

| FIFO Access Time        | t <sub>6</sub> | FIFO READ  | 42   | _    | ns   | 2    |

#### READ Timing (2) (Address/Data Multiplex ADSEL = 1)

Notes: 1. 3-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

2. 2-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

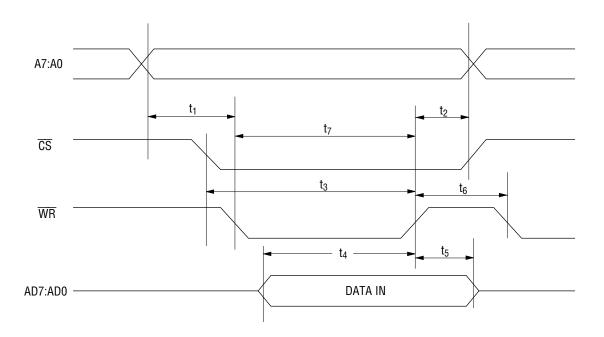

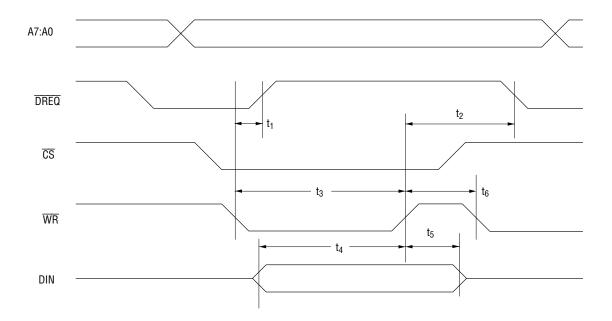

| Parameter                              | Symbol                | Condition  | Min. | Max. | Unit | Note |

|----------------------------------------|-----------------------|------------|------|------|------|------|

| Address Setup Time (WR)                | $t_1(\overline{WR})$  |            | 21   | —    | ns   | 4    |

| Address Setup Time ( $\overline{CS}$ ) | $t_1 (\overline{CS})$ |            | 10   | _    | ns   | 4    |

| Address (CS) Hold Time                 | t <sub>2</sub>        |            | 0    | _    | ns   |      |

| CS Setup Time                          | t <sub>3</sub>        |            | 10   | —    | ns   |      |

| Write Data Setup Time                  | t4                    |            | 30   | —    | ns   |      |

| Write Data Hold Time                   | t <sub>5</sub>        |            | 5    | _    | ns   |      |

| Recovery Time                          | t <sub>6</sub>        | FIFO WRITE | 63   | —    | ns   | 2    |

| FIFO Access Time                       | t7                    | FIFO WRITE | 42   | _    | ns   | 3    |

#### WRITE Timing (1) (Address Separate ADSEL = 0)

Notes: 1.  $t_1$  is defined depending upon  $\overline{CS}$  or  $\overline{WR}$  which becomes active last.

- 2. 3-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

- 3. 2-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

- 4. Either of them should be met.

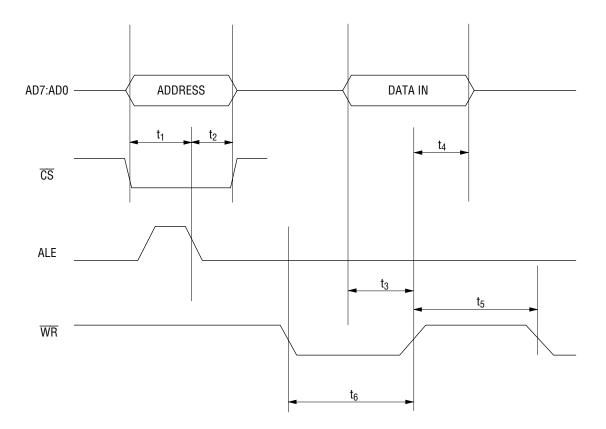

| Parameter               | Symbol         | Condition  | Min. | Max. | Unit | Note |

|-------------------------|----------------|------------|------|------|------|------|

| Address (CS) Setup Time | t1             |            | 10   | _    | ns   |      |

| Address (CS) Hold Time  | t <sub>2</sub> |            | 0    | _    | ns   |      |

| Write Data Setup Time   | t <sub>3</sub> |            | 30   | _    | ns   |      |

| Write Data Hold Time    | t4             |            | 5    | _    | ns   |      |

| Recovery Time           | t <sub>5</sub> | FIFO WRITE | 63   | _    | ns   | 1    |

| FIFO Access Time        | t <sub>6</sub> | FIFO WRITE | 42   | _    | ns   | 2    |

#### WRITE Timing (2) (Address/Data Multiplex ADSEL = 1)

Notes: 1. 3-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

2. 2-clock time of oscillation clock (clock period: 21 ns). It is required for increment of FIFO.

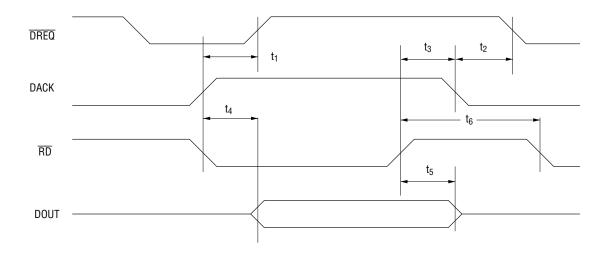

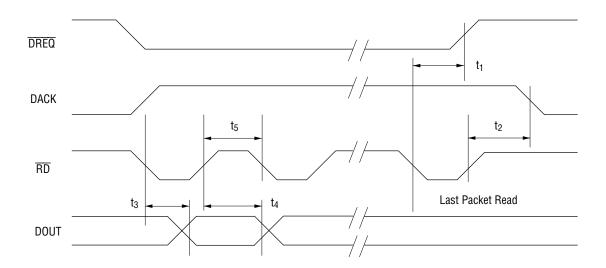

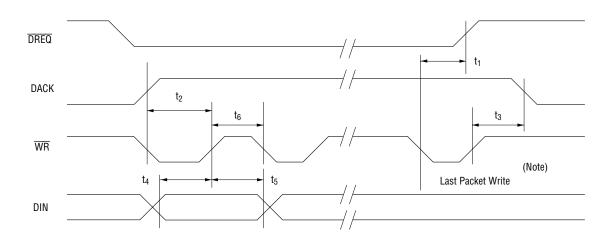

### **DMA Transfer Timing (1)**

| Parameter            | Symbol         | Condition  | Min. | Max. | Unit | Note |

|----------------------|----------------|------------|------|------|------|------|

| DREQ Disable Time    | t <sub>1</sub> | Load 20 pF | —    | 20   | ns   |      |

| DREQ Enable Time     | t <sub>2</sub> |            | —    | 63   | ns   |      |

| DACK Hold Time       | t <sub>3</sub> |            | 0    | _    | ns   |      |

| Read Data Delay Time | t4             | Load 20 pF | _    | 25   | ns   | 1    |

| Data Hold Time       | t <sub>5</sub> |            | 0    | _    | ns   |      |

| Recovery Time        | +              | 8-bit DMA  | 63   | _    | ns   | 2    |

|                      | t <sub>6</sub> | 16-bit DMA | 105  | —    | ns   | 3    |

ML60851A to Memory (Single Transfer, Single Address Mode)

Notes: 1. When in Single Address mode,  $\overline{CS}$  and A7:A0 are ignored.

$t_4$  is defined depending on DACK or  $\overline{RD}$  which becomes active last.

- 2. 3-clock time of oscillation clock (clock period: 21 ns).

- 3. 5-clock time of oscillation clock (clock period: 21 ns).

### DMA Transfer Timing (2)

| Parameter            | Symbol           | Condition  | Min. | Max. | Unit | Note |

|----------------------|------------------|------------|------|------|------|------|

| DREQ Disable Time    | t <sub>1</sub>   | Load 20 pF | _    | 20   | ns   |      |

| DREQ Enable Time     | t <sub>2</sub>   |            |      | 63   | ns   |      |

| Read Data Delay Time | t3               | Load 20 pF | _    | 25   | ns   | 1    |

| Data Hold Time       | t4               |            | 0    | —    | ns   |      |

| Recovery Time        |                  | 8-bit DMA  | 63   | —    | ns   | 2    |

|                      | t <sub>5</sub> – | 16-bit DMA | 105  | _    | ns   | 3    |

ML60851A to Memory (Single Transfer, Dual Address Mode)

Notes: 1. When in Dual Address mode, the DACK is ignored.  $t_3$  is defined depending on  $\overline{CS}$  or  $\overline{RD}$  which becomes active last. A7:A0 specifies the FIFO address. Refer to READ Timing (1) for Address Setup Time and Address Hold Time.

- 2. 3-clock time of oscillation clock (clock period: 21 ns).

- 3. 5-clock time of oscillation clock (clock period: 21 ns).

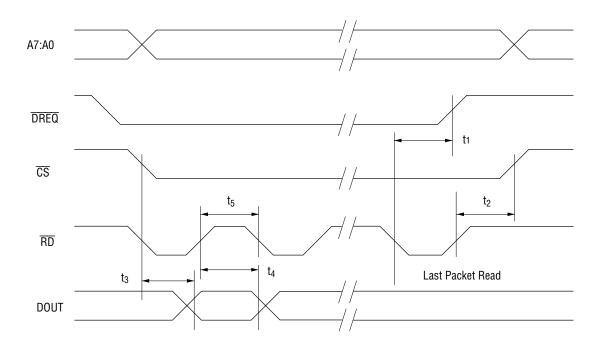

#### **DMA Transfer Timing (3)**

ML60851A to Memory (Demand Transfer, Single Address Mode)

| Parameter            | Symbol           | Condition  | Min. | Max. | Unit | Note |

|----------------------|------------------|------------|------|------|------|------|

| DREQ Disable Time    | t <sub>1</sub>   | Load 20 pF |      | 20   | ns   |      |

| DACK Hold Time       | t2               |            | 0    |      | ns   |      |

| Read Data Delay Time | t <sub>3</sub>   | Load 20 pF | _    | 25   | ns   | 1    |

| Data Hold Time       | t4               |            | 0    |      | ns   |      |

| Recovery Time        |                  | 8-bit DMA  | 63   |      | ns   | 2    |

|                      | t <sub>5</sub> – | 16-bit DMA | 105  |      | ns   | 3    |

Notes: 1. When in Single Address mode,  $t_3$  is defined depending on DACK or  $\overline{RD}$  which becomes active last.

- A7:A0 and  $\overline{CS}$  are ignored.

- 2. 3-clock time of oscillation clock (clock period: 21 ns).

- 3. 5-clock time of oscillation clock (clock period: 21 ns).

### **DMA** Transfer Timing (4)

| ML60851A to Memory (Demand | Transfer, Dual Address Mode) |

|----------------------------|------------------------------|

|----------------------------|------------------------------|

| Parameter            | Symbol           | Condition  | Min. | Max. | Unit | Note |

|----------------------|------------------|------------|------|------|------|------|

| DREQ Disable Time    | t <sub>1</sub>   | Load 20 pF | —    | 20   | ns   |      |

| CS Hold Time         | t <sub>2</sub>   |            | 0    | _    | ns   |      |

| Read Data Delay Time | t <sub>3</sub>   | Load 20 pF | _    | 25   | ns   | 1    |

| Data Hold Time       | t4               |            | 0    | _    | ns   |      |

| Recovery Time        |                  | 8-bit DMA  | 63   | _    | ns   | 2    |

|                      | t <sub>5</sub> – | 16-bit DMA | 105  | _    | ns   | 3    |

Notes: 1. When in Dual Address mode, the DACK is ignored.  $t_3$  is defined depending on  $\overline{CS}$  or  $\overline{RD}$  which becomes active last. A7:A0 specifies the FIFO address. Refer to READ Timing (1) for Address Setup Time and Address Hold Time.

- 2. 3-clock time of oscillation clock (clock period: 21 ns).

- 3. 5-clock time of oscillation clock (clock period: 21 ns).

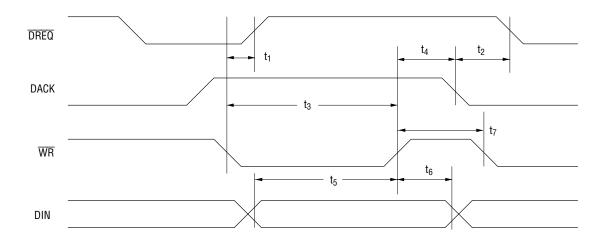

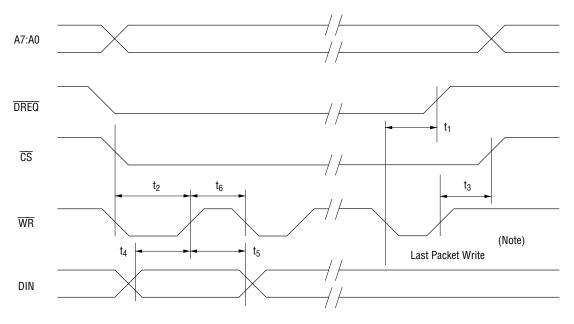

#### **DMA Transfer Timing (5)**

| Parameter             | Symbol           | Condition  | Min. | Max. | Unit | Note |

|-----------------------|------------------|------------|------|------|------|------|

| DREQ Disable Time     | t <sub>1</sub>   | Load 20 pF | —    | 20   | ns   |      |

| DREQ Enable Time      | t <sub>2</sub>   |            | —    | 63   | ns   |      |

| FIFO Access Time      | t <sub>3</sub>   | FIFO WRITE | 42   | _    | ns   | 1    |

| DACK Hold Time        | t4               |            | 0    | _    | ns   |      |

| Write Data Setup Time | t <sub>5</sub>   |            | 30   |      | ns   |      |

| Write Data Hold Time  | t <sub>6</sub>   |            | 5    | —    | ns   |      |

| D                     | +                | 8-bit DMA  | 63   | _    | ns   | 2    |

| Recovery Time         | t <sub>7</sub> – | 16-bit DMA | 105  |      | ns   | 3    |

Memory to ML60851A (Single Transfer, Single Address Mode)

Notes: 1. When in Single Address mode,  $\overline{CS}$  and A7:A0 are ignored.

2. 3-clock time of oscillation clock (clock period: 21 ns).

3. 5-clock time of oscillation clock (clock period: 21 ns).

#### **DMA Transfer Timing (6)**

| Parameter             | Symbol         | Condition  | Min. | Max. | Unit | Note |

|-----------------------|----------------|------------|------|------|------|------|

| DREQ Disable Time     | t <sub>1</sub> | Load 20 pF | _    | 20   | ns   |      |

| DREQ Enable Time      | t <sub>2</sub> |            | _    | 63   | ns   |      |

| FIFO Access Time      | t <sub>3</sub> | FIFO WRITE | 42   | _    | ns   | 1    |

| Write Data Setup Time | t <sub>4</sub> |            | 30   | _    | ns   |      |

| Write Data Hold Time  | t <sub>5</sub> |            | 5    | —    | ns   |      |

| Decover Time          | +              | 8-bit DMA  | 63   | —    | ns   | 2    |

| Recovery Time         | t <sub>6</sub> | 16-bit DMA | 105  | _    | ns   | 3    |

Memory to ML60851A (Single Transfer, Dual Address Mode)

Notes: 1. When in Dual Address mode, the DACK is ignored.

Refer to WRITE Timing (1) for Address Setup Time and Address Hold Time.

- 2. 3-clock time of oscillation clock (clock period: 21 ns).

- 3. 5-clock time of oscillation clock (clock period: 21 ns).

### DMA Transfer Timing (7)

| Parameter             | Symbol         | Condition  | Min. | Max. | Unit | Note |

|-----------------------|----------------|------------|------|------|------|------|

| DREQ Disable Time     | t <sub>1</sub> | Load 20 pF | _    | 20   | ns   |      |

| FIFO Access Time      | t <sub>2</sub> | FIFO WRITE | 42   |      | ns   | 1    |

| DACK Hold Time        | t <sub>3</sub> |            | 0    | _    | ns   |      |

| Write Data Setup Time | t4             |            | 30   | —    | ns   |      |

| Write Data Hold Time  | t <sub>5</sub> |            | 5    |      | ns   |      |

| Dooguary Time         | +              | 8-bit DMA  | 63   | _    | ns   | 2    |

| Recovery Time         | t <sub>6</sub> | 16-bit DMA | 105  | _    | ns   | 3    |

Notes: 1. When in Single Address mode, A7:A0 and  $\overline{CS}$  and ignored.

2. 3-clock time of oscillation clock (clock period: 21 ns).

3. 5-clock time of oscillation clock (clock period: 21 ns).

(Note) The last Write to reach the byte size (maximum packet size) specified by the EP1 Payload Register.

To terminate DMA transfer before reaching the maximum packet size, set EP1 Packet Ready by writing "1" to the EP1 Transmit Packet Ready bit.

#### **DMA Transfer Timing (8)**

| Parameter             | Symbol         | Condition  | Min. | Max. | Unit | Note |

|-----------------------|----------------|------------|------|------|------|------|

| DREQ Disable Time     | t <sub>1</sub> | Load 20 pF | —    | 20   | ns   |      |

| FIFO Access Time      | t <sub>2</sub> | FIFO WRITE | 42   | _    | ns   | 1    |

| CS Hold Time          | t <sub>3</sub> |            | 0    | _    | ns   |      |

| Write Data Setup Time | t <sub>4</sub> |            | 30   | _    | ns   |      |

| Write Data Hold Time  | t <sub>5</sub> |            | 5    | —    | ns   |      |

| Doowery Time          | +              | 8-bit DMA  | 63   | _    | ns   | 2    |

| Recovery Time         | t <sub>6</sub> | 16-bit DMA | 105  |      | ns   | 3    |

Memory to ML60851A (Demand Transfer, Dual Address Mode)

Notes: 1. When in Dual Address mode, the DACK is ignored. A7:A0 specifies the FIFO address. Refer to WRITE Timing (1) for Address Setup Time and Address Hold Time.

- 2. 3-clock time of oscillation clock (clock period: 21 ns).

- 3. 5-clock time of oscillation clock (clock period: 21 ns).

(Note) Refer to the previous page.

# FUNCTIONAL DESCRIPTIONS

# **Pin Functional Description**

#### USB Interface

| Signal | Туре   | Assertion |                                                                                                                                                               | Description |                                                                                           |           |                  |   |   |              |

|--------|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------|-----------|------------------|---|---|--------------|

|        |        |           |                                                                                                                                                               | ( )         | D— signal are the transmitted or received<br>w shows values and results for these signal. |           |                  |   |   |              |

| D.     | 1/0    |           |                                                                                                                                                               | D+          | D-                                                                                        | Result    |                  |   |   |              |

| D+     | D+ I/O | 1/0 —     |                                                                                                                                                               |             |                                                                                           | _         |                  | 0 | 0 | Single end 0 |

|        |        |           |                                                                                                                                                               | -           | 0                                                                                         | 1         | Differential "0" |   |   |              |

|        |        |           |                                                                                                                                                               |             | 1                                                                                         | 0         | Differential "1" |   |   |              |

|        |        |           |                                                                                                                                                               | 1           | 1                                                                                         | Undefined |                  |   |   |              |

| D      | I/O    |           | USB Data (Minus). This signal and the D+ signal are the transmitted or received data from/to USB Bus. The table above shows values and results these signals. |             |                                                                                           |           |                  |   |   |              |

Crystal Oscillator Interface

| Signal | Туре | Assertion | Description                                                                                      |

|--------|------|-----------|--------------------------------------------------------------------------------------------------|

| XIN    | I    | —         | For internal oscillation, connect a crystal to XIN and XOUT.                                     |

| XOUT   | 0    | _         | For external oscillation, supply an external 48 MHz clock signal to XIN.<br>Set XOUT to be open. |

# Application Interface

| Signal  | Туре            | Assertion | Description                                                                             |                                                                        |  |                                                 |

|---------|-----------------|-----------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|-------------------------------------------------|

|         | 1/0             |           | Upper byte (MSB) of data bus. This data bus is used by applications to access           |                                                                        |  |                                                 |

| D15:D8  | I/0             | _         | register files and FIFO data.                                                           |                                                                        |  |                                                 |

|         | AD7:AD0 I/O —   |           | 1/0                                                                                     |                                                                        |  | Lower byte (LSB) of data bus when ADSEL is LOW. |

| AD7:ADU |                 |           | Address and lower byte of data bus are multiplexed when ADSEL is HIGH.                  |                                                                        |  |                                                 |

|         |                 |           | Address when ADSEL is LOW. This address signal is used by application to                |                                                                        |  |                                                 |

| A7:A0   | 1               | _         | access register files and FIFO data.                                                    |                                                                        |  |                                                 |

|         |                 |           | This signal is ignored (all lows or all highs) when ADSEL is HIGH.                      |                                                                        |  |                                                 |

| CS      |                 |           | Chip Select. When this signal is asserted LOW, the ML60851A is selected                 |                                                                        |  |                                                 |

| 65      |                 | LOW       | and ready to read or write data.                                                        |                                                                        |  |                                                 |

|         | RD I            |           | LOW                                                                                     | Read Strobe. When this signal is asserted LOW, the Read instruction is |  |                                                 |

| RD      |                 | LUW       | executed.                                                                               |                                                                        |  |                                                 |

|         |                 |           | Write Strobe. When this signal is asserted LOW, the Write instruction is                |                                                                        |  |                                                 |

| WR      |                 | I LOW     | executed.                                                                               |                                                                        |  |                                                 |

|         | 0               | LOW       | Interrupt Request. When this signal is asserted, the ML60851A makes an                  |                                                                        |  |                                                 |

| INTR    | INTR 0 (Note 1) |           | interrupt request to the application.                                                   |                                                                        |  |                                                 |

| DREQ    | 0               | LOW       | DMA Request. This signal requests the Endpoint FIFO to make a DMA transfer.             |                                                                        |  |                                                 |

| DREQ    |                 | (Note 1)  |                                                                                         |                                                                        |  |                                                 |

| DAOK    |                 |           | HIGH                                                                                    | DMA Acknowledge Signal. This signal, when asserted, enables accessing  |  |                                                 |

| DACK    |                 | (Note 1)  | FIFOs, without address bus setting.                                                     |                                                                        |  |                                                 |

|         |                 |           | When ADSEL is HIGH, the address and $\overline{\text{CS}}$ on AD7:AD0 is latched at the |                                                                        |  |                                                 |

| ALE     |                 | _         | trailing edge of this signal. This signal is ignored when ADSEL is LOW.                 |                                                                        |  |                                                 |

|         |                 |           | When ADSEL is LOW, the address is input on A7:A0 and data i input on                    |                                                                        |  |                                                 |

| ADSEL   | 1               | I   —     | D15:D8 and AD7:AD0. When ADSEL is HIGH, the lower bytes (LSB) of                        |                                                                        |  |                                                 |

|         |                 |           | address and data are multiplexed on AD7:AD0.                                            |                                                                        |  |                                                 |

| RESET   |                 |           | System Reset. When this signal is asserted LOW, the ML60851A is reset.                  |                                                                        |  |                                                 |

| RESEI   |                 | I LOW     | When the ML60851A is powered on, this signal must be asserted for 1 $\mu$ s.            |                                                                        |  |                                                 |

$Note: \ \ 1. \ \ Initial value immediately after resetting. \ Its assertion can be changed by programming.$

#### **Functional Description**

The ML60851A USB device controller contains the Protocol Engine, DPLL, Timer, Status/Control, FIFO Control, Application Interface, and Remote Wakeup blocks.

- Protocol Engine

The Protocol Engine handles the USB communication protocol. It performs control of packet transmission/reception, generation/detection of synchronous patterns, CRC generation/checking, NRZI data modulation, bit stuffing, and packet ID (PID) generation/checking.

- DPLL (Digital Phase Locked Loop) The DPLL extracts clock and data from the USB differential received data (D+ and D–).

- Timer The Timer block monitors idle time on the USB bus.

- Status/Control

The Status Control block moniors the transaction status and transmits control events to the application through an interrupt request.

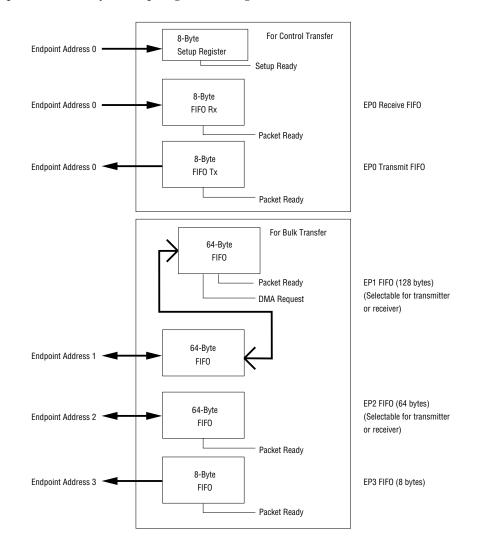

#### FIFO Control

The FIFO Control block controls all FIFO operations for transmitting and receiving USB packets. The FIFO configuration is described below.

Endpoint FIFO/8-Byte Setup Register Configuration

| FIFO type              | Endpoint address | Program size        | Function             |

|------------------------|------------------|---------------------|----------------------|

| Reception              | 0                | 8 Bytes             | Transfer control     |

| Transmission           | 0                | 8 Bytes             | Transfer control     |

| Reception/Transmission | 1                | 64 Bytes (2 levels) | Bulk-In and bulk-Out |

| Reception/Transmission | 2                | 64 Bytes            | Bulk-Out and bulk-In |

| Transmission           | 3                | 8 Bytes             | Interrupt            |

Every FIFO has a flag that indicates a full or empty FIFO and the capability of re-transmitting and re-receiving data. Endpoint addresses 1 and 2 can be used for either of reception and transmission by writing the register.

The FIFO at endpoint address 1 can be used for DMA transfer.

#### • Interrupt

Interrupt factors include Packet Ready for a transmit/receive FIFO, Setup Ready for 8-byte setup data, and Suspend. Generation of each interrupt request can be enabled or disabled by the Interrupt Enable register.

#### • DMA

8-bit and 16-bit demand transfer DMA and single transfer DMA are enabled for bulk-transfer FIFO at endpoint address 1.

In Demand Transfer mode, DREQ is asserted when a valid packet arrives at the FIFO. When the external DMA contoller has completed transferring all byte data of a received packet, DREQ is deasserted. Accordingly, other devices cannot access the local bus during DMA transfer.

In Single Tranfer mode, each time transfer of one byte data is completed, DREQ is deasserted. While DREQ is deasserted, other devices can access the local bus.

• Remote Wakeup

This functional block supports the remote wakeup function.

• USB Transfers

The ML60851A supports the two transfer types (Control Transfer and Bulk Transfer) of four transfer types (Control, Isochronous, Interrupt, and Bulk) defined by the USB Specifications.

- The Control Transfer is required for transfer of configuration, commands, and status information between the host and devices.

- The Bulk Transfer enables transfer of a large amount of data when the bus bandwidth is enough.

- USB Transceiver

The ML60851A contains an Oki's USB transceiver which converts internal unidirectional signals into USB-compatible signals.

This enables the designer's application module to interface to the physical layer of the USB.

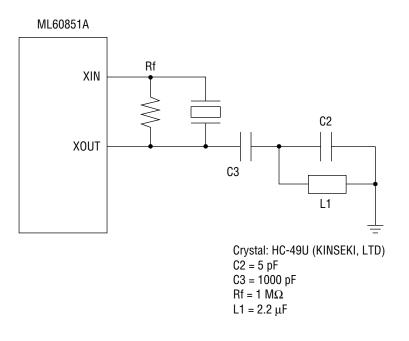

# **EXAMPLE OF OSCILLATOR CIRCUIT**

Note: The example indicated above is not guaranteed for circuit operation.

# PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1998 Oki Electric Industry Co., Ltd.